在高度发展的现代工业中,现代测试技术向数字化、信息化方向发展已成为必然发展趋势。振动传感器可用于机械中的振动和位移、转子与机壳的热膨胀量的长期监测;生产线的在线自动检测和自动控制;科学研究中的多种微小距离和微小运动的测量等。振动传感器常应用于能源、化工、医学、汽车、冶金,机器制造,军工,科研教学等诸多领域。

单位时间内位移的增量就是速度。速度包括线速度和角速度,与之相对应的就有线速度传感器和角速度传感器,我们都统称为速度传感器。

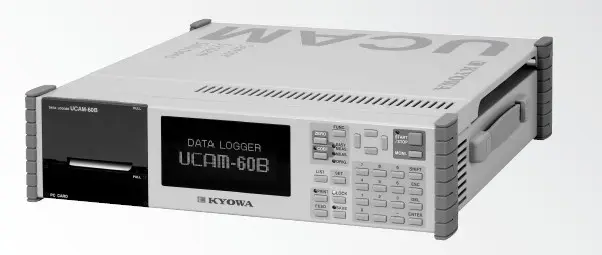

数据采集仪,是指便携轻便的数据采集器/图形记录仪,可以同时测量10通道的温/湿度,模拟电压。 通过宽大的彩色屏幕,客户在测试时更容易清楚的看到捕获的数据和轻松设置参数来观测波形和数据。通过功能可以更容易再现捕获的数据,并且可以保存到仪器内存或外部USB存储器里。标准的PC USB接口通过软件来控制,是客户很好的选择。

射频功率扩大器(RF PA)是各种无线发射机的重要组成部分。在发射机的前级电路中,调制振荡电路所发生的射频信号功率很小,需求经过一系列的扩大一缓冲级、中间扩大级、末级功率扩大级,取得足够的射频功率今后,才干馈送到天线上辐射出去。为了取得足够大的射频输出功率,有必要选用射频功率扩大器。

采集器是由微处理器控制的智能设备,是该系统的主要设备之一。它的功能是收集多个电表的电脉冲信号并将其转换成数字数据进行记录和保存,因此简称数据采集器。